揭秘读卡器芯片天梯图:智能卡技术的关键发展路径与未来方向探索

- 问答

- 2025-11-04 09:04:18

- 6

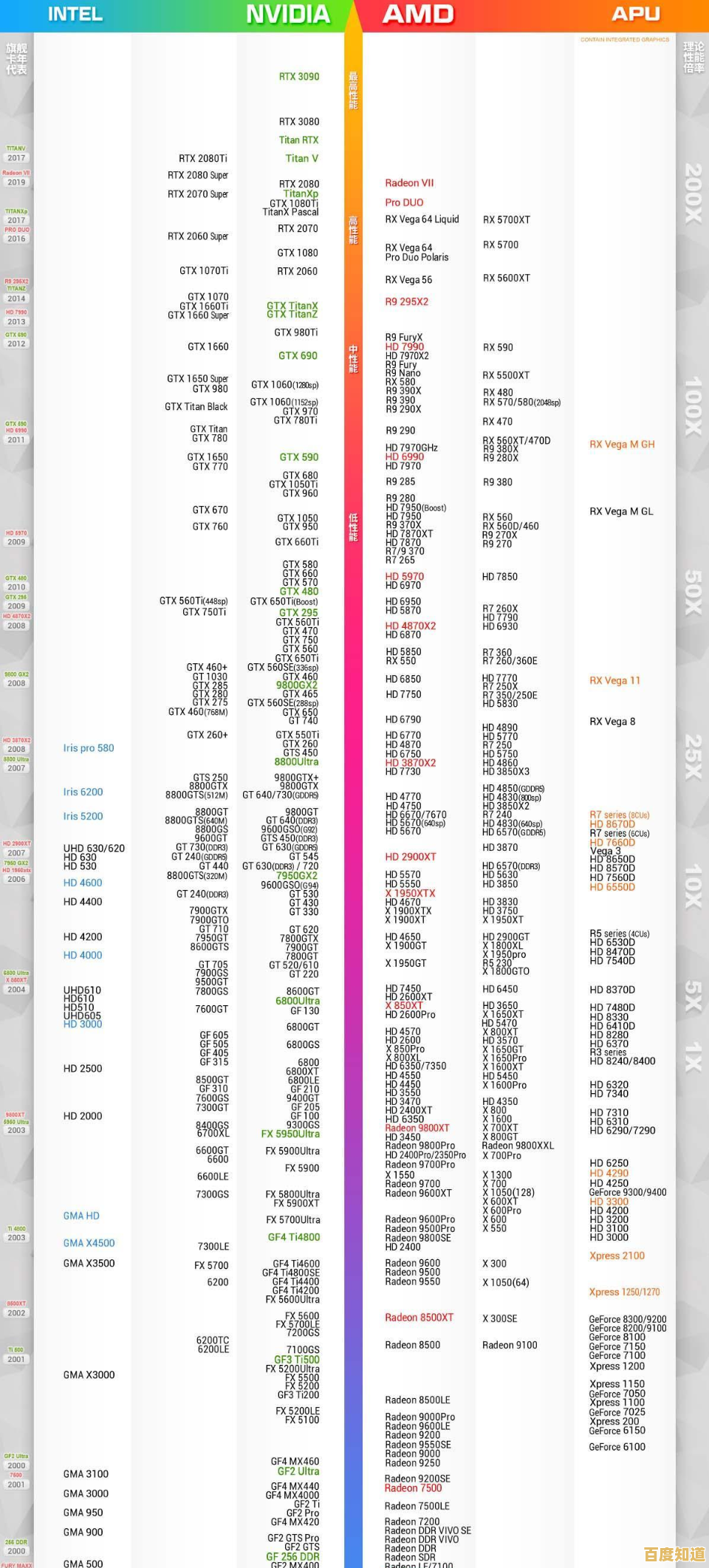

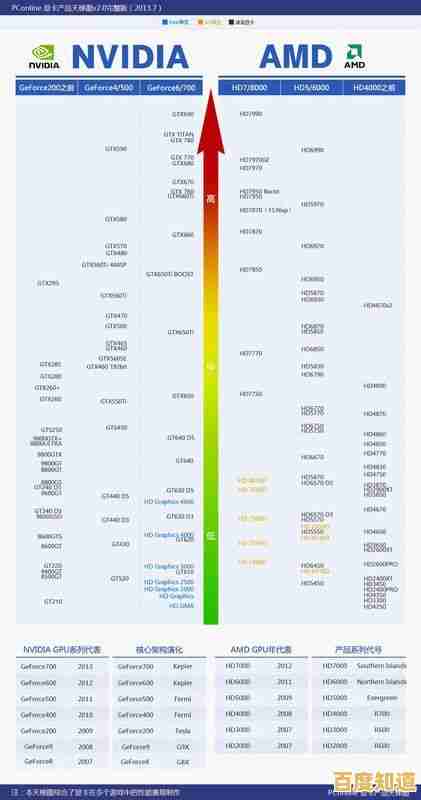

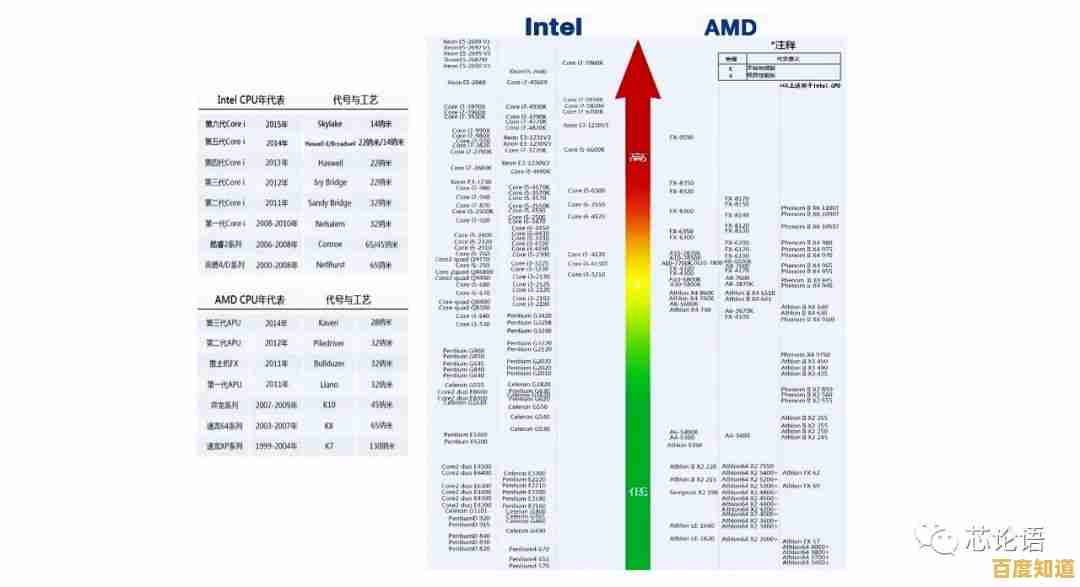

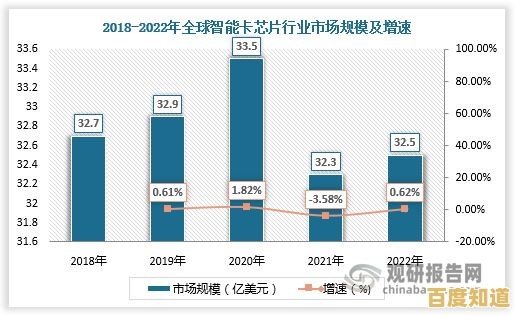

“读卡器芯片天梯图”这个概念,并非一个官方发布的权威排名,更像是技术爱好者或行业内人士为了更直观地理解不同芯片性能层级而创造的一种比喻,它形象地将各种读卡器芯片按照其处理能力、安全性、功能复杂度和适用场景,从低到高进行排列,就像游戏显卡或手机处理器的性能天梯图一样,要理解这张“天梯图”,我们必须回溯智能卡技术本身的发展之路。

早期的基石:接触式与基础安全

智能卡技术的起点是接触式芯片卡,最典型的代表就是我们曾经广泛使用的银行卡或SIM卡,根据国际标准ISO/IEC 7816的定义,这类卡需要通过物理触点与读卡器连接,此时的读卡器芯片,技术路径相对单纯,核心任务是完成稳定的数据传输和基础的安全认证,它的“天梯”层级主要由处理简单加密算法(如DES、3DES)的能力、通信速率和可靠性决定,这类芯片构成了天梯图最宽广的底层,支撑着大量对实时性要求不高、但需要基本安全保障的应用,如门禁卡、预付费电卡等。

关键的跃升:非接触式与速度革命

随着城市一卡通、第二代身份证以及NFC手机的普及,非接触式技术(遵循ISO/IEC 14443标准)将智能卡技术推上了一个新台阶,这一阶段的读卡器芯片发生了质变,它不再需要物理接触,通过射频场进行无线供电和数据交换,这对芯片提出了极高要求:需要集成高频模拟电路、高效的电源管理单元以及更复杂的通信协议栈,在天梯图上,支持非接触通信的芯片无疑站上了更高的层级,它们的性能指标主要体现在读写距离、数据传输速率(从106kbps发展到如今的848kbps甚至更高)以及多标签同时识别的防冲突能力上,这一时期,恩智浦半导体(NXP)的MIFARE系列芯片因其先发优势和成熟生态,在全球交通、门禁领域占据了重要位置。

安全为王:金融级与国密算法

当智能卡进入金融支付领域(如银联“闪付”),安全成为了读卡器芯片天梯图的终极考核标准,遵循EMV(Europay, Mastercard, Visa)标准的金融支付读卡器芯片,处于天梯图的顶尖层级,它们必须能够处理极其复杂的公钥加密算法(如RSA、ECC),具备高级别的防攻击能力(如侧信道攻击、故障注入攻击),并通过PCI PTS等严苛的安全认证,另一个关键发展路径是国密算法的集成,支持SM1、SM2、SM4等国密算法的读卡器芯片,成为国内政务、金融、关键基础设施领域的硬性要求,这类芯片不仅技术难度高,还涉及国家信息安全战略,因此在特定的“天梯”路径上占据了制高点。

融合与智能化:多功能集成与物联网未来

当前,读卡器芯片的发展路径正朝着高度集成和智能化迈进,单一功能的芯片逐渐被淘汰,未来的“天梯图”顶端属于多功能融合芯片,一颗先进的读卡器SoC(片上系统)可能同时支持接触式、非接触式(ISO14443 A/B、Felica)、NFC卡模拟、条码扫描甚至指纹识别,它们不仅是读卡器,更是物联网设备的边缘计算节点,一款智能POS机的芯片,除了处理支付交易,还能运行操作系统、管理显示屏、连接4G/5G和Wi-Fi,随着物联网的爆发,对超高频(UHF)读卡器芯片(遵循ISO/IEC 18000-63标准,用于远距离物品追踪)的需求也日益增长,这构成了天梯图中一条平行的、专注于远距离、多标签读取的技术路径。

未来方向探索

展望未来,读卡器芯片的天梯图将继续演变。安全性无止境,后量子密码学(PQC)可能会成为下一代芯片应对量子计算威胁的新标准。AI的集成是一个明确方向,芯片内嵌AI加速器,可以实现本地化的生物特征识别(如人脸、静脉)与卡认证的融合,提升安全性和便捷性。无缝体验将是关键,读卡器芯片将更深度地与手机、汽车、智能家居等设备融合,实现“无感”的认证与支付。绿色节能也将成为重要考量,通过优化芯片设计和制程工艺,降低功耗,以适应更广泛的物联网应用场景。

读卡器芯片的“天梯图”生动描绘了技术从满足基本功能,到追求便捷高效,再到捍卫安全可信,最终迈向智能融合的发展脉络,它不是一个静态的排名,而是一个动态演进的技术路线图,其每一步升级都紧密呼应着社会生活和产业升级的实际需求。

(注:文中提到的技术标准如ISO/IEC 7816、ISO/IEC 14443、EMV、PCI PTS等,以及公司如NXP,均为行业公开信息和通用技术规范。)

本文由姓灵阳于2025-11-04发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://shandong.xlisi.cn/wenda/71048.html